В Сети появились снимки непростого графического ядра AMD Fiji

Исследовательская компания Chipworks опубликовала фотографию ядра AMD Fiji

Исследовательская компания Chipworks опубликовала фотографию ядра (die shot) графического процессора AMD Fiji, который используется на адаптерах серии AMD Radeon R9 Fury. Подобные снимки позволяют получить некоторое представление о внутреннем устройстве микросхемы и сделать определённые выводы о технологиях.

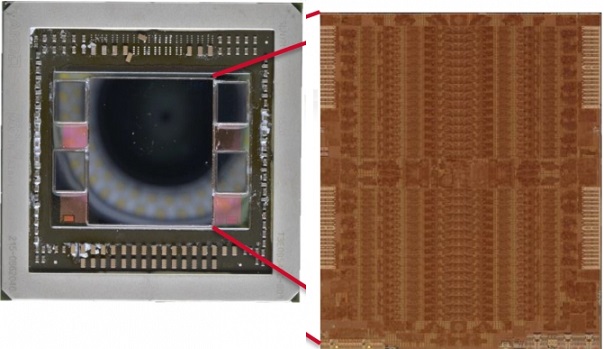

На снимке ядра Fiji, полученном компанией Chipworks при помощи растрового электронного микроскопа (РЭМ, англ. scanning electron microscope, SEM), можно заметить основные области GPU, отвечающие за различные операции. К сожалению, качество снимка не позволяет с уверенностью сказать, где находятся конкретные исполнительные устройства, а также достоверно определить их количество. Однако даже такой снимок даёт некоторые представления о внутреннем устройстве AMD Fiji.

ФОТО: Графический процессор AMD Fiji

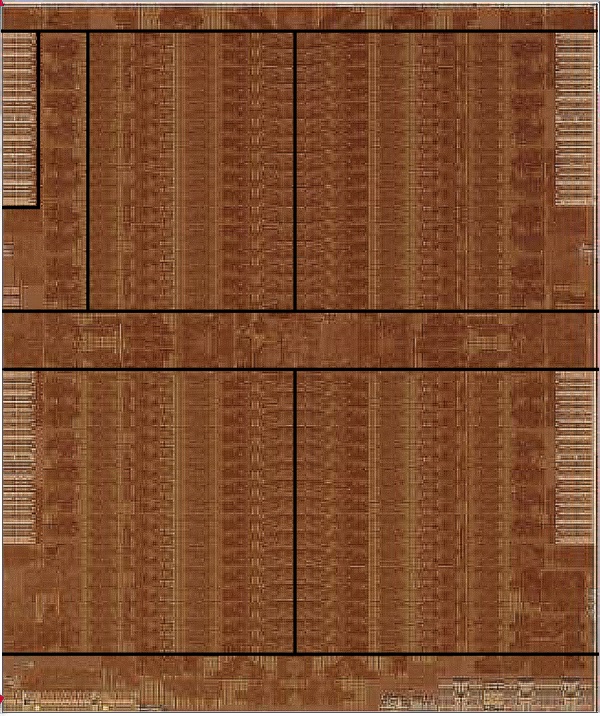

Фотография ядра Fiji показывает, что новый флагманский графический процессор AMD по-прежнему условно разделён на четыре кластера из потоковых процессоров (stream processors, SPs), блоков текстурирования (texture units, TUs.), конвейеров растеризации (raster operations pipelines, ROPs), кешей второго уровня (L2) и контроллеров памяти (memory controllers, MCs). Принимая во внимание архитектурные особенности, следует понимать, что блоки ROP, MC и L2 не принадлежат конкретным вычислительным кластерам, а работают относительно автономно. Тем не менее, достоверно определить, что является ROP, а что — контроллером памяти, на снимке такого качества невозможно. Примечательно, что верхние и нижние кластеры на снимке не являются симметричными.

ФОТО: Снимок ядра графического процессора AMD Fiji с предполагаемой разметкой основных блоков.

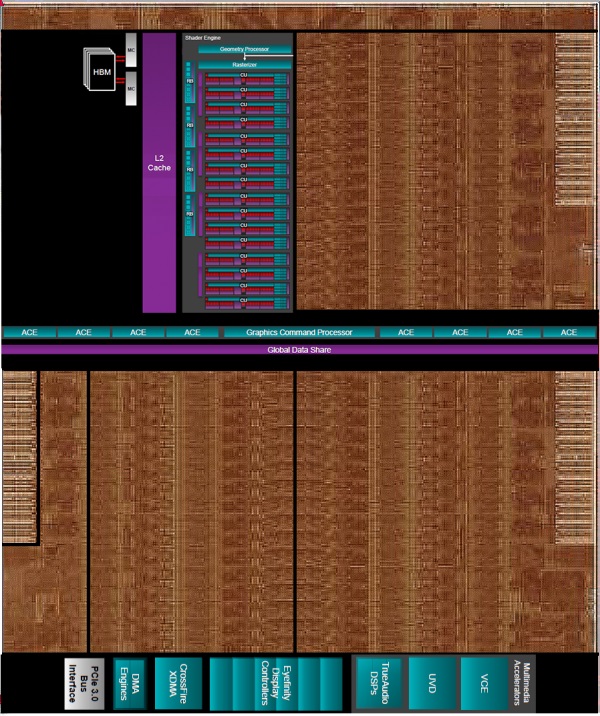

В середине GPU располагается командный процессор (command processor), управляющий работой всей микросхемы; четыре блока асинхронных вычислений ACE (asynchronous compute engine) и два улучшенных блока асинхронных вычислений HWS (на некоторых диаграммах отображаются как четыре блока ACE, чтобы подчеркнуть их повышенную эффективность), которые позволяют запускать на одном GPU несколько приложений одновременно. Контроллеры памяти и четыре 1024-разрядных физических интерфейса для подключения памяти HBM (high bandwidth memory) располагаются на боковых сторонах микросхемы, рядом с блоками ROP. Мультимедийные ускорители (модули декодирования и отображения (масштабирования) видео (VCE, UVD)), контроллеры дисплеев, цифровые сигнальные процессоры TrueAudio, интерфейс CrossFire XDMA, DMA логика и интерфейс PCI Express 3.0 расположены в нижней части чипа (на блок-диаграммах Fiji из презентаций AMD они располагаются сбоку).

Снимок ядра графического процессора AMD Fiji с наименованиями основных блоков.

Примечательно, что хотя 1024-разрядные физические интерфейсы памяти HBM имеют огромное количество контактов, их физический размер сравним с таковым у 64-разрядных интерфейсов памяти GDDR5. Данное преимущество обеспечивается использованием дорогостоящих кремниевых соединительных подложек (silicon interposer), которые производятся при помощи фотолитографического оборудования по технологии с шириной транзисторного затвора 65 нм.

В целом, физические интерфейсы — будь то интерфейсы памяти, или же PCI Express — по-прежнему занимают существенную часть площади ядра. Тем не менее, использование HBM даёт возможность сократить количество интерфейсов и контроллеров памяти внутри графического процессора, что даёт возможность увеличить количество исполнительных устройств (например, потоковых процессоров, или специализированных блоков) без увеличения себестоимости.

Блок-схема графического процессора AMD Fiji.

Компоновка AMD Fiji характерна для всех высокопроизводительных GPU на базе архитектуры GCN, поскольку позволяет оптимально организовать обмен данными, а также оптимизировать энергопотребление и выделяемый тепловой поток. Существует большая вероятность, что AMD Greenland сохранит аналогичную схему размещения различных устройств внутри графического процессора.

Происшествия «РФ наразі готується до нового наземного штурму на південному сході України, – ГУР»

Происшествия «РФ наразі готується до нового наземного штурму на південному сході України, – ГУР»  Общество «Похолодание, дожди и заморозки: прогноз погоды в Украине на следующую неделю»

Общество «Похолодание, дожди и заморозки: прогноз погоды в Украине на следующую неделю»  Происшествия «412-та бригада Nemesis показала новий рівень інтеграції безпілотних сил України»

Происшествия «412-та бригада Nemesis показала новий рівень інтеграції безпілотних сил України»  Общество «Фітофтороз, парша й гнилі: як уберегти картоплю народними засобами»

Общество «Фітофтороз, парша й гнилі: як уберегти картоплю народними засобами»  Происшествия «Сили оборони "змагаються" з окупантами за трьома напрямками, – Сирський»

Происшествия «Сили оборони "змагаються" з окупантами за трьома напрямками, – Сирський»  Происшествия «У районі Часового Яру зірвано прорив військ РФ, – 24 ОМБр»

Происшествия «У районі Часового Яру зірвано прорив військ РФ, – 24 ОМБр»